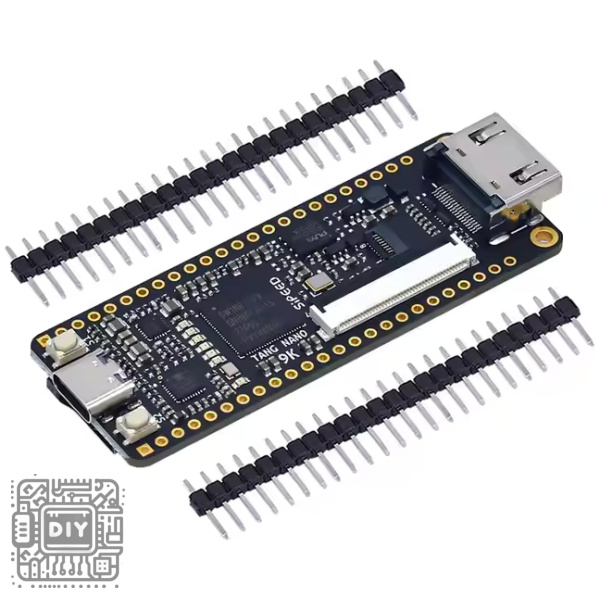

Sipeed Tang Nano 9K FPGA Board

35,000 د.ع

Build and explore digital logic designs with the Sipeed Tang Nano 9K FPGA Development Board, a compact yet powerful platform based on the Gowin GW1NR-9 FPGA chip. This versatile board is designed for beginners learning FPGA development, as well as experienced engineers working on complex digital circuits, RISC-V softcore implementations, and video processing applications. With 8,640 logic units, onboard memory, and multiple display interfaces, the Tang Nano 9K offers exceptional value for FPGA experimentation and prototyping

In stock

CompareDescription

Sipeed Tang Nano 9K FPGA Development Board – Gowin GW1NR-9 with 8640 LUTs

Build and explore digital logic designs with the Sipeed Tang Nano 9K FPGA Development Board, a compact yet powerful platform based on the Gowin GW1NR-9 FPGA chip. This versatile board is designed for beginners learning FPGA development, as well as experienced engineers working on complex digital circuits, RISC-V softcore implementations, and video processing applications. With 8,640 logic units, onboard memory, and multiple display interfaces, the Tang Nano 9K offers exceptional value for FPGA experimentation and prototyping.

The board is built around the Gowin GW1NR-9 FPGA, featuring 8,640 LUT4 logic cells, 6,480 flip-flops, 468 Kbits of block SRAM, and 20 DSP slices for 18×18-bit multiplication. The onboard 64 Mbit PSRAM and 32 Mbit SPI flash provide ample storage for complex designs and bitstream storage. A 27 MHz crystal oscillator with two integrated PLLs enables flexible clock generation for high-speed applications.

A standout feature of the Tang Nano 9K is its rich set of display interfaces, including HDMI output, RGB LCD interface, and SPI screen interface, making it ideal for video processing and display driver projects. The onboard BL702 chip provides integrated USB-JTAG and USB-UART functionality, allowing programming and debugging through a single USB-C cable without external programmers. Additional features include a microSD card slot for data storage, six programmable LEDs, two user buttons, and 2×24-pin 2.54mm expansion headers for GPIO access.

The board is fully supported by the free Gowin EDA software, which provides a complete FPGA development environment with synthesis, place-and-route, and programming tools. Whether you’re implementing a RISC-V softcore, building a retro gaming console, or learning digital design fundamentals, the Tang Nano 9K delivers the features and performance needed for your FPGA projects.

Key Features

Powerful Gowin GW1NR-9 FPGA

Powered by the Gowin GW1NR-9 FPGA chip featuring 8,640 LUT4 logic cells, 6,480 flip-flops, 468 Kbits of block SRAM, 64 Mbit PSRAM, and 20 DSP slices, providing substantial resources for complex digital designs and softcore processors.

Rich Display Interfaces

Features HDMI output, RGB LCD interface, and SPI screen interface, enabling a wide range of video and display applications including retro gaming emulators, video processing, and GUI development.

Onboard Memory Resources

Integrates 64 Mbit PSRAM for data-intensive applications and 32 Mbit SPI flash for storing FPGA bitstreams, providing ample storage for complex designs and boot configurations.

Built-in USB-JTAG and USB-UART

Onboard BL702 chip provides USB-JTAG and USB-UART functionality, allowing bitstream downloading, debugging, and serial communication through a single USB-C cable without external programmers.

Flexible Clock Management

Features a 27 MHz onboard crystal oscillator with two integrated PLLs, enabling flexible clock generation for high-speed applications and timing-critical designs.

MicroSD Card Slot

Built-in microSD card slot provides removable storage for data logging, firmware updates, and ROM files, essential for retro gaming emulators and data-intensive applications.

User Interface and Expansion

Provides six user-controllable LEDs, two programmable push buttons, and 2×24-pin 2.54mm expansion headers with GPIO, SPI, I2C, and power signals for peripheral expansion.

Compact Form Factor

Measures approximately 65mm x 23mm with USB-C connectivity, making it easy to integrate into projects and breadboards while maintaining a small footprint.

Gowin IDE Support

Fully supported by Gowin EDA, a free and user-friendly FPGA development environment with fast synthesis times, IP core generation, and comprehensive documentation.

Specifications

| Parameter | Value |

|---|---|

| FPGA Chip | Gowin GW1NR-9 |

| Logic Units (LUT4) | 8,640 |

| Flip-Flops (FF) | 6,480 |

| Block SRAM | 468 Kbits |

| PSRAM | 64 Mbits |

| SPI Flash | 32 Mbits |

| DSP Slices (18×18) | 20 |

| PLLs | 2 |

| Crystal Oscillator | 27 MHz |

| Display Interfaces | HDMI, RGB LCD, SPI Screen |

| Storage | microSD card slot |

| User Interface | 6 LEDs, 2 push buttons |

| Debugger | Onboard BL702 |

| Expansion | 2×24-pin 2.54mm headers |

| Power Supply | 5V via USB-C |

| Dimensions | Approximately 65mm x 23mm |

Wiring Diagram

Basic Power and Programming

USB-C Cable -----> Board USB-C Port (Provides 5V power and programming via onboard JTAG/UART)

Connecting a Display

HDMI Cable -----> Board HDMI Port or RGB LCD -----> RGB FPC Connector or SPI Display -----> SPI FPC Connector

Storage Expansion

microSD Card -----> Board microSD Slot

Development Environment Setup

Gowin IDE Installation

Download Gowin EDA from the Gowin Semiconductor website

Install the software following the installation wizard

Request a free license

Launch Gowin IDE and create a new project

Select the device: GW1NR-9C / GW1NR-LV9QN88PC6/I5

Programming the Board

Connect the Tang Nano 9K to your computer via USB-C

The board will be recognized as a JTAG programmer

In Gowin IDE, synthesize and place-and-route your design

Assign pins using the Floor Planner tool

Click “Program” to download the bitstream to the FPGA

Example Code

LED Blink Test (Verilog)

module led_blink ( input wire clk_27m, input wire rst_n, output reg [5:0] led ); reg [24:0] counter; always @(posedge clk_27m or negedge rst_n) begin if (!rst_n) begin counter <= 0; led <= 6'b000000; end else begin counter <= counter + 1; if (counter == 27_000_000) begin counter <= 0; led <= led + 1; end end end endmodule

Common Applications

Retro gaming console emulation

RISC-V softcore processor experimentation

Digital signal processing and audio synthesis

Video processing and HDMI output

Embedded system prototyping and education

Custom hardware acceleration

Display driver development

FPGA learning and digital design education

Package Contents

1 x Sipeed Tang Nano 9K FPGA Development Board

لوحة تطوير FPGA Sipeed Tang Nano 9K – معالج Gowin GW1NR-9 بسعة 8640 LUT

ابنِ واستكشف التصاميم المنطقية الرقمية باستخدام لوحة تطوير FPGA Sipeed Tang Nano 9K، وهي منصة مدمجة وقوية تعتمد على شريحة Gowin GW1NR-9 FPGA. تم تصميم هذه اللوحة متعددة الاستخدامات للمبتدئين الذين يتعلمون تطوير FPGA، وكذلك للمهندسين ذوي الخبرة الذين يعملون على دوائر رقمية معقدة وتنفيذ المعالجات الناعمة RISC-V وتطبيقات معالجة الفيديو. مع 8,640 وحدة منطقية وذاكرة مدمجة وواجهات عرض متعددة، تقدم Tang Nano 9K قيمة استثنائية لتجارب FPGA والنمذجة الأولية.

تم بناء اللوحة حول شريحة Gowin GW1NR-9 FPGA، التي تتميز بـ 8,640 خلية منطقية LUT4، و 6,480 فلوب فلوب، و 468 كيلوبت من ذاكرة SRAM الكتلية، و 20 شريحة DSP للضرب 18×18 بت. توفر ذاكرة PSRAM 64 ميجابت وذاكرة الفلاش SPI 32 ميجابت المدمجة تخزينًا وافرًا للتصاميم المعقدة وتخزين الـ bitstream. يتيح مذبذب بلوري 27 ميجاهرتز مع حلقتا PLL مدمجتان توليد ساعة مرنة للتطبيقات عالية السرعة.

الميزة البارزة في Tang Nano 9K هي مجموعة واجهات العرض الغنية، بما في ذلك مخرج HDMI وواجهة شاشة RGB LCD وواجهة شاشة SPI، مما يجعلها مثالية لمعالجة الفيديو ومشاريع مشغلات الشاشات. توفر شريحة BL702 المدمجة وظائف USB-JTAG و USB-UART مدمجة، مما يسمح بالبرمجة وتصحيح الأخطاء عبر كابل USB-C واحد بدون مبرمجين خارجيين. تشمل الميزات الإضافية فتحة بطاقة microSD لتخزين البيانات، وستة مصابيح LED قابلة للبرمجة، وزرين للمستخدم، ورؤوس توسعة 2×24 دبوس بمسافة 2.54 مم للوصول إلى GPIO.

اللوحة مدعومة بالكامل بواسطة برنامج Gowin EDA المجاني، الذي يوفر بيئة تطوير FPGA كاملة مع أدوات التوليف والتخطيط والبرمجة. سواء كنت تنفذ معالج RISC-V ناعمًا أو تبني وحدة تحكم ألعاب قديمة أو تتعلم أساسيات التصميم الرقمي، فإن Tang Nano 9K تقدم الميزات والأداء الذي تحتاجه لمشاريع FPGA الخاصة بك.

المميزات الرئيسية

معالج Gowin GW1NR-9 FPGA القوي

مدعوم بشريحة Gowin GW1NR-9 FPGA التي تتميز بـ 8,640 خلية منطقية LUT4، و 6,480 فلوب فلوب، و 468 كيلوبت من ذاكرة SRAM الكتلية، و 64 ميجابت PSRAM، و 20 شريحة DSP، مما يوفر موارد كبيرة للتصاميم الرقمية المعقدة والمعالجات الناعمة.

واجهات عرض غنية

يتميز بمخرج HDMI وواجهة شاشة RGB LCD وواجهة شاشة SPI، مما يتيح مجموعة واسعة من تطبيقات الفيديو والشاشات بما في ذلك محاكيات ألعاب الريترو ومعالجة الفيديو وتطوير واجهات المستخدم الرسومية.

موارد ذاكرة مدمجة

يدمج 64 ميجابت PSRAM للتطبيقات المكثفة للبيانات و 32 ميجابت SPI فلاش لتخزين bitstream FPGA، مما يوفر تخزينًا وافرًا للتصاميم المعقدة وتكوينات التمهيد.

USB-JTAG و USB-UART مدمجان

توفر شريحة BL702 المدمجة وظائف USB-JTAG و USB-UART، مما يسمح بتنزيل الـ bitstream وتصحيح الأخطاء والتواصل التسلسلي عبر كابل USB-C واحد بدون مبرمجين خارجيين.

إدارة ساعة مرنة

يتميز بمذبذب بلوري 27 ميجاهرتز مع حلقتا PLL مدمجتان، مما يتيح توليد ساعة مرنة للتطبيقات عالية السرعة والتصاميم الحرجة للتوقيت.

فتحة بطاقة microSD

فتحة بطاقة microSD مدمجة توفر تخزينًا قابلاً للإزالة لتسجيل البيانات وتحديثات البرامج الثابتة وملفات ROM، ضرورية لمحاكيات ألعاب الريترو والتطبيقات المكثفة للبيانات.

واجهة مستخدم وتوسعة

توفر ستة مصابيح LED يمكن التحكم بها، وزرين ضغط قابلين للبرمجة، ورؤوس توسعة 2×24 دبوس بمسافة 2.54 مم مع إشارات GPIO و SPI و I2C والطاقة لتوسعة المحيطات.

عامل شكل مضغوط

قياسات حوالي 65 مم × 23 مم مع اتصال USB-C، مما يسهل دمجها في المشاريع ولوحات التجارب مع الحفاظ على بصمة صغيرة.

دعم بيئة Gowin IDE

مدعومة بالكامل بواسطة Gowin EDA، بيئة تطوير FPGA المجانية مع أوقات توليف سريعة وتوليد نوى IP وتوثيق شامل.

المواصفات الفنية

| المعلمة | القيمة |

|---|---|

| شريحة FPGA | Gowin GW1NR-9 |

| الوحدات المنطقية (LUT4) | 8,640 |

| Flip-Flops (FF) | 6,480 |

| ذاكرة SRAM الكتلية | 468 كيلوبت |

| PSRAM | 64 ميجابت |

| SPI فلاش | 32 ميجابت |

| شرائح DSP (18×18) | 20 |

| حلقات قفل الطور (PLL) | 2 |

| مذبذب البلورة | 27 ميجاهرتز |

| واجهات العرض | HDMI، RGB LCD، SPI Screen |

| التخزين | فتحة microSD |

| واجهة المستخدم | 6 مصابيح LED، 2 زر |

| المصحح | BL702 مدمج |

| التوسعة | رؤوس 2×24 دبوس 2.54 مم |

| الطاقة | 5V عبر USB-C |

| الأبعاد | حوالي 65 مم × 23 مم |

التطبيقات الشائعة

محاكاة أجهزة ألعاب الريترو

تجارب المعالج الناعم RISC-V

معالجة الإشارات الرقمية وتركيب الصوت

معالجة الفيديو وإخراج HDMI

نمذجة أولية للأنظمة المدمجة والتعليم

تسريع الأجهزة المخصصة

تطوير مشغلات الشاشات

تعلم FPGA والتصميم الرقمي

محتويات العلبة

1 × لوحة تطوير FPGA Sipeed Tang Nano 9K

Reviews

There are no reviews yet